# **PIXELPLUS**

# PCC030K 0.3MP Product Brief

### The PCC030K is single chip of CIS and ISP. It is a low-cost, high-performance analog and digital image sensor designed specifically for rear view camera applications.

The PCC030K is a 1/6.62-inch CMOS image sensor with NTSC/PAL transmitter. It is a single chip with an effective pixel array of 644 (width) x 484 (height) in an ultra-compact module size, making it an ideal camera solution for rear-view systems.

The PCC030K can generate a digital/composite data at maximum frame rate of 60 FPS. On-chip sensor functions can be controlled through I2C interface.

The output interface of PCC030K is DVP 8-bit, CVBS It supports auto black level compensation, horizontal/vertical mirroring, automatic flicker cancellation.

Typical value

3.4 um x 3.4 um

644(H) x 484(V)

1/6.62 inch

27 MHz

CVBS

60 fps

54 sec@60[°C]

34K [e/lux\*sec]

2.189 mm x 1.645 mm

DVP 8-bit Raw RGB Bayer 8-bit YCbCr422 8-bit

Y only 8-bit

NTSC

PAL

**Technical Specifications**

Parameter

Effective pixel array

Effective image area

Input clock frequency

**Optical format**

Output interface

Max. frame rate

Dark signal

Sensitivity

Pixel size

### Applications

Rear view camera

### Product Features

- 644x484 effective pixel array with RGB bayer color filters and micro-lens

- Output Interface : DVP 8-bit, CVBS

- Auto black level compensation support

- Horizontal/vertical mirroring support

- Image processing on chip : lens shading compensation, gamma correction, defect correction, color correction, NR(2D noise reduction), color interpolation, edge enhancement, brightness, contrast, de-color, auto white balance, auto exposure control, back light compensation, color saturation

- Automatic flicker cancellation support

- On-chip phase locked loop(PLL)

- I2C interface(master/slave) support

- Crystal input support

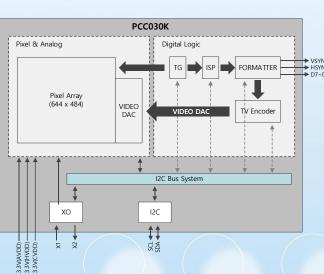

## Functional Block Diagram

| Power supply                                | AVDD 3.3V, IO 3.3V, CVDD 3.3V                                             |

|---------------------------------------------|---------------------------------------------------------------------------|

| Power consumption                           | 200 [mW] @ dynamic(CVBS)<br>125 [mW] @ dynamic(DVP)<br>660 [uW] @ standby |

| Operating temp.<br>(Fully functional temp.) | - 40 [°C] ~ 85 [°C] (Ambient)                                             |

| Dynamic range                               | 64 [dB]                                                                   |

| SNR                                         | 45 [dB]                                                                   |

| Package type                                | CSP 20ball                                                                |

| al Logic                                    | → VSYNC<br>→ HSYNC<br>→ D7-D0                                             |

| IDEO DAC TV Encoder                         |                                                                           |

## PIXELPLUS

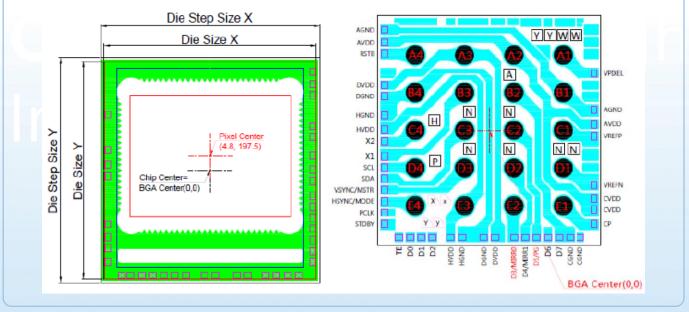

## Pad and ball formation

Package size : 2937 um x 3008 um 20 ball

### Package ball assignment table

| Ball | Ball           | I/O  | Pull up/  | DAD description                                                                                                                                                                                                            |

|------|----------------|------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ball | name           | type | pull down | PAD description                                                                                                                                                                                                            |

| A1   | VPIXEL         | 0    | -         | PIXEL VDD.<br>It should be tied with nearby AGND by both 1uF bypass capacitors.                                                                                                                                            |

| A2   | AVDD           | Р    | -         | Analog VDD 3.3V                                                                                                                                                                                                            |

| A3   | DVDD           | Р    | -         | Digital(core) VDD 1.2V DC (internal LDO output)                                                                                                                                                                            |

| A4   | RSTB           | I    | Pullup    | System reset must remain low for at least 8 master clocks after power is stabilized.<br>When the sensor is reset, all registers are set to their default values.                                                           |

| B1   | AGND           | Р    |           | Analog GND                                                                                                                                                                                                                 |

| B2   | CGND           | Р    | -         | VDAC GND                                                                                                                                                                                                                   |

| B3   | X1             | I    | -         | Crystal input pad or master clock input pad                                                                                                                                                                                |

| B4   | HGND/<br>DGND  | Ρ    | -         | IO GND / digital(core) GND                                                                                                                                                                                                 |

| C1   | VREFP          | 0    | <b>N-</b> | PCP output.<br>It should be tied with nearby RGND by both 1uF bypass capacitors.                                                                                                                                           |

| C2   | D5/PG          | BIO  | Pulldown  | Digital output bit 5 / strap input pad : PG mode                                                                                                                                                                           |

| C3   | SDA            | BIO  | Pullup    | 2-wire serial interface data, SDA line is pulled up to HVDD by off-chip resistor.                                                                                                                                          |

| C4   | X2             | 0    | -         | Crystal output pad                                                                                                                                                                                                         |

| D1   | VREFN          | 0    | -         | NCP output.<br>It should be tied with nearby RGND by both 1uF bypass capacitors.                                                                                                                                           |

| D2   | D4/MIRR1       | BIO  | Pullup    | Digital output bit 4/ strap input pad : mirror mode[1]                                                                                                                                                                     |

| D3   | VSYNC/<br>MSTR | BIO  | Pullup    | Vertical synchronization pulse. VSYNC indicates the start of a new frame / MSTR is the strap input pad for master mode.                                                                                                    |

| D4   | SCL            | BIO  | Pullup    | 2-wire serial interface clock, SCL line is pulled up to HVDD by off-chip resistor.                                                                                                                                         |

| E1   | СР             | 0    | -         | Composite differential positive signal<br>Make the total resistance value to 37.5ohm(or 75ohm according to register setting)                                                                                               |

| E2   | D3/MIRR0       | BIO  | Pulldown  | Digital output bit 3 / strap input pad : mirror mode[0]                                                                                                                                                                    |

| E3   | HVDD           | Р    | -         | IO VDD 3.3V DC                                                                                                                                                                                                             |

| E4   | HSYNC/<br>MODE | BIO  | Pullup    | Horizontal synchronization pulse. HSYNC is high(or low) for the horizontal window of interest. It can be programmed to appear or not outside the vertical window of interest / MODE is the strap input pad for frame mode. |

### Crystal Image through Imaging Innovation