# PK9210K 2.0MP Product Brief

The PK9210K has excellent noise performance for low light condition and high dynamic range support by 2-exp line based HDR mode up to 120dB

The PK9210K is the 1/2.92" RGB bayer CMOS image sensor (CIS) designed to support 2.0MP at 30 frames per second (fps). The PK9210K consists of 1960 (H) x 1120 (V) effective pixels with 12 added active pixels on each side and 8 pixels on each side for color interpolation.

The PK9210K has excellent noise performance for low light condition and high dynamic range (HDR) support using by DCG (Dual Conversion Gain) and multi- exposure method up to 120dB. It incorporates on-chip CIS functions such as Defective Pixel Correction (DPC), Purple Fringing Reduction (PFR), exposure control, HDR combine reconstruction, and so on. It enables the PK9210K shows no saturation image in the worst contrast

The PK9210K is suitable for a rear view camera and surroundview camera, home appliances and security applications with excellent image quality with 2.8V/1.8V/1.2V power supply.

#### **Applications**

- Rear View Camera

- 360° Surround View Monitoring System (SVM)

- Security

- Home appliances

#### **Product Features**

- Support for display image size 1920 x 1080 with 2.0MP

- Support for HDR 120 dB with DCG and multi exposure.

- Support for combined RGB bayer output format

- ISP function: LSC, DPC, PFR, HDR combination, automatic black level correction, compression, etc

- Programmable frame size, window size, and exposure

- External synchronization support (Genlock)

- One-time programmable memory (OTP)

- Active Dummy Array for offset correction

- Spread Spectrum Clock Generation (SSCG)

#### **Technical Specifications**

| Parameter                   | Typical value                               |

|-----------------------------|---------------------------------------------|

| Pixel size                  | 2.8 um x 2.8 um                             |

| Effective pixel array       | 1960(H) x 1120(V)                           |

| Effective image area        | 5.4880 mm x 3.1360 mm                       |

| Optical format              | 1/2.92 inch                                 |

| CRA                         | 23.7 °                                      |

| Input clock frequency       | 27 MHz                                      |

| Output interface            | 2-Lane MIPI / DVP Combo                     |

| Max. frame rate             | HDR 30 fps only                             |

| Dark Current                | 23 e-/sec @60℃                              |

| Sensitivity                 | 30.3K e-/Lux. sec                           |

|                             | HVDD: 1.8 ~ 2.8V                            |

| Power supply                | AVDD : 2.8 V                                |

|                             | DVDD : 1.2 V                                |

| Power consumption @30fps    | DPV : 204mW / 234mW<br>MIPI : 201mW / 202mW |

| (HVDD = 1.8V / HVDD = 2.8V) | Standby : 2mW /2mW                          |

| Operating temp.             | -40 ~ 105 °C (Ambient)                      |

| Max. dynamic range          | 120 dB                                      |

| SNR                         | 44 dB @60℃                                  |

| Package type                | NeoPAC I / APLGA / 64CLCC                   |

| Package size(mm)            | 7.6 x 5.86 / 8.34 x 6.45 / 11.1 x 11.1      |

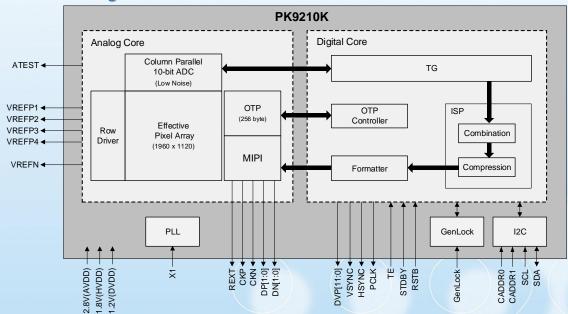

### Functional Block Diagram

PIXELPLUS

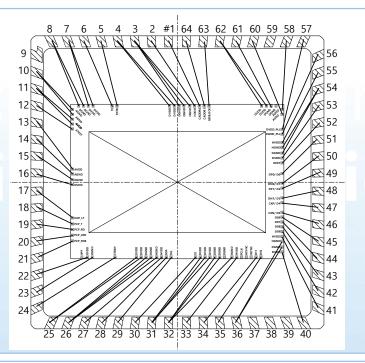

64CLCC Ball Map

lmag

### 64CLCC Ball Description

| Ball | Ball Name  | Ю | Pull up/<br>Pull down | Ball Description                                                                                                                                              |

|------|------------|---|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | CADDR0     | I | pullup                | Chip address bit 0                                                                                                                                            |

| 2    | HVDD       | Р | -                     | IO VDD 1.8V~2.8V DC It should be tied with nearby HGND by 1uF bypass capacitors.                                                                              |

| 3    | HGND, DGND | Р | -                     | IO GND / Digital(Core) GND                                                                                                                                    |

| 4    | DVDD       | Р | -                     | Digital(Core) VDD 1.2V DC It should be tied with nearby DGND by 1uF bypass capacitors.                                                                        |

| 5    | RSTB       | I | pullup                | System reset must remain low for at least 8 master clocks after power is stabilized. When the sensor is reset, all registers are set to their default values. |

| 6    | TE         | 1 | pulldown              | Chip test mode enable                                                                                                                                         |

| 7    | DVDD       | Р | -                     | Digital(Core) VDD 1.2V DC It should be tied with nearby DGND by 1uF bypass capacitors.                                                                        |

| 8    | DGND       | Р | -                     | Digital(Core) GND                                                                                                                                             |

| 9    | AGND       | Р | -                     | Analog GND                                                                                                                                                    |

| 10   | AVDD       | Р |                       | Analog VDD 2.8V<br>It should be tied with nearby AGND by both 1uF bypass capacitors.                                                                          |

| 11   | ATEST      | 0 | <b>y</b> . [          | Analog test output                                                                                                                                            |

| 12   | AVDD       | Р | -                     | Analog VDD 2.8V<br>It should be tied with nearby AGND by both 1uF bypass capacitors.                                                                          |

| 13   | AGND       | Р | -                     | Analog GND                                                                                                                                                    |

| 14   | DGND       | Р | -                     | Digital(Core) GND                                                                                                                                             |

| 15   | DVDD       | Р |                       | Digital(Core) VDD 1.2V DC It should be tied with nearby DGND by 1uF bypass capacitors.                                                                        |

| 16   | VREFN1     | 0 | -                     | VREFN1 output. It should be tied with nearby AGND by 1uF bypass capacitors.                                                                                   |

| 17   | VREFP1     | 0 | -                     | VREFP1 output. It should be tied with nearby AGND by 1uF bypass capacitors.                                                                                   |

| 18   | VREFP2     | 0 | -                     | VREFP2 output. It should be tied with nearby AGND by 1uF bypass capacitors.                                                                                   |

| 19   | VREFP3     | 0 | -                     | VREFP3 output. It should be tied with nearby AGND by 1uF bypass capacitors.                                                                                   |

| 20   | VREFP4     | 0 | -                     | VREFP4 output. It should be tied with nearby AGND by 1uF bypass capacitors.                                                                                   |

| Ball     | Ball Name          | 10     | Pull up/<br>Pull down | Ball Description                                                                                                                                                                                                                                             |

|----------|--------------------|--------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21       | NC                 | -      | -                     | -                                                                                                                                                                                                                                                            |

| 22       | NC                 | -      | -                     | -                                                                                                                                                                                                                                                            |

| 23       | OVDD               | Р      | -                     | Analog VDD 2.8V for OTP It should be tied with nearby OGND by 1uF bypass capacitors.                                                                                                                                                                         |

| 24       | OGND               | Р      | _                     | Analog GND for OTP                                                                                                                                                                                                                                           |

|          |                    |        |                       | Power stdby mode. When Stdby ='1', there's no current flow in any analog                                                                                                                                                                                     |

| 25       | STDBY              | I      | pulldown              | circuit branch, neither any beat of digital clock.  Digital(Core) VDD 1.2V DC                                                                                                                                                                                |

| 26       | DVDD               | Р      | -                     | It should be tied with nearby DGND by 1uF bypass capacitors.                                                                                                                                                                                                 |

| 27       | DGND, HGND         | Р      | -                     | Digital(Core) GND / IO GND                                                                                                                                                                                                                                   |

| 28       | HVDD               | Р      | -                     | IO VDD 1.8V~2.8V DC It should be tied with nearby HGND by 1uF bypass capacitors.                                                                                                                                                                             |

| 29       | SDA                | BIO    | pullup                | 2-wire serial interface clock, SDA line is pulled up to HVDD by off-chip resistor                                                                                                                                                                            |

| 30       | SCL                | BIO    | pullup                | 2-wire serial interface data, SCL line is pulled up to HVDD by off-chip resistor                                                                                                                                                                             |

| 31       | X1                 | I      | pulldown              | Master clock input pad                                                                                                                                                                                                                                       |

| 32       | DVDD               | Р      | -                     | Digital(Core) VDD 1.2V DC It should be tied with nearby DGND by 1uF bypass capacitors.                                                                                                                                                                       |

| 33       | HVDD               | Р      | -                     | IO VDD 1.8V ~ 2.8V DC It should be tied with nearby DGND by 1uF bypass capacitors.                                                                                                                                                                           |

| 34       | DGND, HGND         | Р      | -                     | Digital(Core) GND / IO GND                                                                                                                                                                                                                                   |

|          | HVDD               | Р      | -                     | IO VDD 1.8V~2.8V DC It should be tied with nearby HGND by 1uF bypass capacitors.                                                                                                                                                                             |

| 35       | D11                | 0      | pulldown              | Digital Output bit 11                                                                                                                                                                                                                                        |

| 36       | D10                | 0      | pulldown              | Digital Output bit 10                                                                                                                                                                                                                                        |

| 37       | DGND, HGND         | Р      | -                     | Digital(Core) GND / IO GND                                                                                                                                                                                                                                   |

| 38       | NC                 | -      | -                     | -                                                                                                                                                                                                                                                            |

| 39       | NC                 | -      | -                     | -                                                                                                                                                                                                                                                            |

| 40       | DVDD               | Р      | -                     | Digital(Core) VDD 1.2V DC<br>It should be tied with nearby DGND by 1uF bypass capacitors.                                                                                                                                                                    |

| 41       | HVDD               | Р      | -                     | IO VDD 1.8V~2.8V DC It should be tied with nearby HGND by 1uF bypass capacitors.                                                                                                                                                                             |

| 42       | D9                 | 0      | pulldown              | Digital Output bit 9                                                                                                                                                                                                                                         |

| 43       | D8                 | 0      | pulldown              | Digital Output bit 8                                                                                                                                                                                                                                         |

| 44       | D7                 | 0      | pulldown              | Digital Output bit 7                                                                                                                                                                                                                                         |

| 45       | D6                 | 0      | pulldown              | Digital Output bit 6                                                                                                                                                                                                                                         |

| 46       | CKN/D5             | 0      | pulldown              | MIPI Clock Negative Output / Digital Output bit 5                                                                                                                                                                                                            |

| 47       | CKP/D4             | 0      | pulldown              | MIPI Clock Positive Output / Digital Output bit 4                                                                                                                                                                                                            |

| 48       | DN1/D3             | 0      | pulldown              | MIPI DN1 Output / Digital Output bit 3                                                                                                                                                                                                                       |

| 49       | DP1/D2             | 0      | pulldown              | MIPI DP1 Output / Digital Output bit 2                                                                                                                                                                                                                       |

| 50       | DN0/D1             | 0      | pulldown              | MIPI DN0 Output / Digital Output bit 1                                                                                                                                                                                                                       |

| 51       | DP0/D0             | 0      | pulldown              | MIPI DP0 Output / Digital Output bit 0                                                                                                                                                                                                                       |

| 52       | REXT               | 0      | -                     | External Resistor for MIPI Digital(Core) VDD 1.2V DC                                                                                                                                                                                                         |

| 53<br>54 | DVDD<br>DGND, HGND | P<br>P | -                     | It should be tied with nearby DGND by 1uF bypass capacitors.  Digital(Core) GND / IO GND                                                                                                                                                                     |

| 55       | HVDD               | P      | -                     | IO VDD 1.8V~2.8V DC It should be tied with nearby HGND by 1uF bypass capacitors.                                                                                                                                                                             |

| 56       | DGND_PLL           | Р      | -                     | PLL GND                                                                                                                                                                                                                                                      |

| 57       | DVDD_PLL           | Р      |                       | PLL VDD 1.2V DC It should be tied with nearby DGND PLL by 1uF bypass capacitors.                                                                                                                                                                             |

| 58       | AGND               | Р      | -                     | Analog GND                                                                                                                                                                                                                                                   |

| 59       | NC                 | _      | -                     | -                                                                                                                                                                                                                                                            |

| 60       | AVDD               | Р      | -                     | Analog VDD 2.8V<br>It should be tied with nearby AGND by both 1uF bypass capacitors.                                                                                                                                                                         |

| 61       | DGND               | Р      | -                     | Digital(Core) GND                                                                                                                                                                                                                                            |

| 62       | DVDD               | Р      | -                     | Digital(Core) VDD 1.2V DC<br>It should be tied with nearby DGND by 1uF bypass capacitors.                                                                                                                                                                    |

| 63       | GENLOCK            | BIO    | pulldown              | External Frame sync input. Slave chip can receive the external frame sync signal from master chip/External Frame sync output. Master chip can output the external frame sync signal through this pad to synchronize all digital outputs of two or more chips |

| 64       | CADDR1             | I      | pullup                | Chip address bit 1                                                                                                                                                                                                                                           |

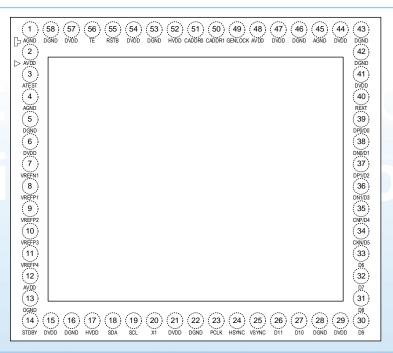

## APLGA Ball Map

| #9        | #8        | #7        | #6     | #5     | #4   | #3   | #2     | #1     | $\angle$ |

|-----------|-----------|-----------|--------|--------|------|------|--------|--------|----------|

| NC        | DVDD      | GENLOCK   | CADDR1 | HVDD   | DVDD | RSTB | TE     | NC     | #G       |

| DVDD_PLL  | AVDD      | AGND      | DVDD   | CADDRO | vss  | DVDD | DVDD   | ATEST  | #F       |

| DPO/D0    | DNO/D1    | REXT      | vss    | vss    | vss  | vss  | AGND   | AVDD   | #E       |

| DP1/D2    | DN1/D3    | <b>D6</b> | vss    | HSYNG  | vss  | vss  | vss    | VREFP1 | #[       |

| CKP/D4    | CKN/D5    | <b>D7</b> | VSYNC  | SCL    | DVDD | vss  | VREFP2 | VREFN1 | #(       |

| <b>D8</b> | <b>D9</b> | DVDD      | PCLK   | vss    | SDA  | HVDD | VREFP3 | VREFP4 | #E       |

| (NC)      | (D10)     | (D11)     | vss    | (X1)   | vss  | vss  | STDBY  | (NC)   | #/       |

## APLGA Ball Description

| Ball | Ball Name | 10  | Pull up/<br>Pull down | Ball Description                                                                                                            |

|------|-----------|-----|-----------------------|-----------------------------------------------------------------------------------------------------------------------------|

| A2   | STDBY     | I   | pulldown              | Power stdby mode. When Stdby ='1', there's no current flow in any analog circuit branch, neither any beat of digital clock. |

| A3   | VSS       | Р   | -                     | Digital (Core) GND, IO GND                                                                                                  |

| A4   | VSS       | Р   | -                     | Digital (Core) GND, IO GND                                                                                                  |

| A5   | X1        | I   | pulldown              | Master clock input pad                                                                                                      |

| A6   | VSS       | Р   | -                     | Digital (Core) GND, IO GND                                                                                                  |

| A7   | D11       | 0   | pulldown              | Digital Output bit 11                                                                                                       |

| A8   | D10       | 0   | pulldown              | Digital Output bit 10                                                                                                       |

| B1   | VREFP4    | 0   |                       | VREFP4 output. It should be tied with nearby AGND by 1uF bypass capacitors.                                                 |

| B2   | VREFP3    | 0   | - 1                   | VREFP3 output. It should be tied with nearby AGND by 1uF bypass capacitors.                                                 |

| В3   | HVDD      | Р   | <b>U</b> . I          | IO VDD 1.8V ~ 2.8V DC It should be tied with nearby DGND by 1uF bypass capacitors.                                          |

| B4   | SDA       | BIO | pullup                | 2-wire serial interface clock, SDA line is pulled up to HVDD by off-chip resistor                                           |

| B5   | VSS       | Р   | -                     | Digital (Core) GND, IO GND                                                                                                  |

| В6   | PCLK      | 0   | pulldown              | PAD clock Data can be latched by external devices at the rising or falling edge of PCLK                                     |

| В7   | DVDD      | Р   | -                     | Digital (Core) VDD 1.2V DC It should be tied with nearby DGND by 1uF bypass capacitors.                                     |

| B8   | D9        | 0   | pulldown              | Digital Output bit 9                                                                                                        |

| В9   | D8        | 0   | pulldown              | Digital Output bit 8                                                                                                        |

| C1   | VREFN1    | 0   | -                     | VREFN1 output. It should be tied with nearby AGND by 1uF bypass capacitors.                                                 |

| C2   | VREFP2    | 0   | -                     | VREFP2 output. It should be tied with nearby AGND by 1uF bypass capacitors.                                                 |

| C3   | VSS       | Р   | -                     | Digital (Core) GND, IO GND                                                                                                  |

| C4   | DVDD      | Р   | -                     | Digital (Core) VDD 1.2V DC It should be tied with nearby DGND by 1uF bypass capacitors.                                     |

| Ball | Ball Name | Ю   | Pull up/<br>Pull down | Ball Description                                                                                                                                                                                                                                              |  |  |  |

|------|-----------|-----|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| C5   | SCL       | BIO | pullup                | 2-wire serial interface data, SCL line is pulled up to HVDD by off-chip resistor                                                                                                                                                                              |  |  |  |

| C6   | VSYNC     | 0   | pulldown              | Vertical sync : Indicates the start of a new frame                                                                                                                                                                                                            |  |  |  |

| C7   | D7        | 0   | pulldown              | Digital Output bit 7                                                                                                                                                                                                                                          |  |  |  |

| C8   | CKN/D5    | 0   | pulldown              | MIPI Clock Negative Output / Digital Output bit 5                                                                                                                                                                                                             |  |  |  |

| С9   | CKP/D4    | 0   | pulldown              | MIPI Clock Positive Output / Digital Output bit 4                                                                                                                                                                                                             |  |  |  |

| D1   | VREFP1    | 0   | -                     | VREFP1 output. It should be tied with nearby AGND by 1uF bypass capacitors.                                                                                                                                                                                   |  |  |  |

| D2   | VSS       | Р   | -                     | Digital (Core) GND, IO GND                                                                                                                                                                                                                                    |  |  |  |

| D3   | VSS       | Р   | -                     | Digital (Core) GND, IO GND                                                                                                                                                                                                                                    |  |  |  |

| D4   | VSS       | Р   | -                     | Digital (Core) GND, IO GND                                                                                                                                                                                                                                    |  |  |  |

| D5   | HSYNC     | 0   | pulldown              | Horizontal synchronization pulse. HSYNC is high (or low) for the horizontal window of int erest. It can be programmed to appear or not outside the vertical window of interest.                                                                               |  |  |  |

| D6   | VSS       | Р   | -                     | Digital (Core) GND, IO GND                                                                                                                                                                                                                                    |  |  |  |

| D7   | D6        | 0   | pulldown              | Digital Output bit 6                                                                                                                                                                                                                                          |  |  |  |

| D8   | DN1/D3    | 0   | pulldown              | MIPI DN1 Output / Digital Output bit 3                                                                                                                                                                                                                        |  |  |  |

| D9   | DP1/D2    | 0   | pulldown              | MIPI DP1 Output / Digital Output bit 2                                                                                                                                                                                                                        |  |  |  |

| E1   | AVDD      | Р   | -                     | Analog VDD 2.8V It should be tied with nearby AGND by 1uF bypass capacitors.                                                                                                                                                                                  |  |  |  |

| E2   | AGND      | Р   | -                     | Analog GND                                                                                                                                                                                                                                                    |  |  |  |

| E3   | VSS       | P   | -                     | Digital (Core) GND, IO GND                                                                                                                                                                                                                                    |  |  |  |

| E4   | VSS       | P   |                       | Digital (Core) GND, IO GND                                                                                                                                                                                                                                    |  |  |  |

| E5   | VSS       | P   |                       | Digital (Core) GND, IO GND                                                                                                                                                                                                                                    |  |  |  |

| E6   | VSS       | P   | _                     | Digital (Core) GND, IO GND                                                                                                                                                                                                                                    |  |  |  |

| E7   | REXT      | 0   |                       | External Resistor for MIPI                                                                                                                                                                                                                                    |  |  |  |

| E8   | DNO/D1    | 0   | pulldown              | MIPI DNO Output / Digital Output bit 1                                                                                                                                                                                                                        |  |  |  |

| E9   | DPO/D0    | 0   | pulldown              | MIPI DPO Output / Digital Output bit 0                                                                                                                                                                                                                        |  |  |  |

| F1   | ATEST     | 0   | -                     | Analog test output                                                                                                                                                                                                                                            |  |  |  |

| F2   | DVDD      | Р   | -                     | Digital (Core) VDD 1.2V DC  It should be tied with nearby DGND by 1uF bypass capacitors.                                                                                                                                                                      |  |  |  |

| F3   | DVDD      | Р   |                       | Digital (Core) VDD 1.2V DC It should be tied with nearby DGND by 1uF bypass capacitors.                                                                                                                                                                       |  |  |  |

| F4   | VSS       | Р   |                       | Digital (Core) GND, IO GND                                                                                                                                                                                                                                    |  |  |  |

| F5   | CADDRO    |     | pullup                | Chip address bit 0                                                                                                                                                                                                                                            |  |  |  |

| F6   | DVDD      | Р   | -                     | Digital (Core) VDD 1.2V DC  It should be tied with nearby DGND by 1uF bypass capacitors.                                                                                                                                                                      |  |  |  |

| F7   | AGND      | Р   |                       | Analog GND                                                                                                                                                                                                                                                    |  |  |  |

| F8   | AVDD      | P   |                       | Analog VDD 2.8V It should be tied with nearby AGND by 1uF bypass capacitors.                                                                                                                                                                                  |  |  |  |

| F9   | DVDD_PLL  | Р   | -                     | PLL VDD 1.2V DC  It should be tied with hearby DGND_PLL by 1uF bypass capacitors                                                                                                                                                                              |  |  |  |

| G2   | TE        | 1   | pulldown              | Chip test mode enable                                                                                                                                                                                                                                         |  |  |  |

| GZ   | IE        | I   | pulluowii             |                                                                                                                                                                                                                                                               |  |  |  |

| G3   | RSTB      | I   | pullup                | System reset must remain low for at least 8 master clocks after power is stabilized. Whe n the sensor is reset, all registers are set to their default values.                                                                                                |  |  |  |

| G4   | DVDD      | Р   | -                     | Digital (Core) VDD 1.2V DC It should be tied with nearby DGND by 1uF bypass capacitors.                                                                                                                                                                       |  |  |  |

| G5   | HVDD      | Р   | -                     | IO VDD 1.8V $^{\sim}$ 2.8V DC It should be tied with nearby DGND by 1uF bypass capacitors.                                                                                                                                                                    |  |  |  |

| G6   | CADDR1    | I   | pullup                | Chip address bit 1                                                                                                                                                                                                                                            |  |  |  |

| G7   | GENLOCK   | BIO | pulldown              | External Frame sync input. Slave chip can receive the external frame sync signal from ma ster chip/External Frame sync output. Master chip can output the external frame sync signal through this pad to synchronize all digital outputs of two or more chips |  |  |  |

| G8   | DVDD      | Р   | -                     | Digital (Core) VDD 1.2V DC It should be tied with nearby DGND by 1uF bypass capacitors.                                                                                                                                                                       |  |  |  |

NeoPAC I Ball Map

lmag

### NeoPAC | Ball Description

| Ball | Ball Name | 10  | Pull up/<br>Pull down | Ball Description                                                                                                             |  |  |  |  |

|------|-----------|-----|-----------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1    | AGND      | Р   | -                     | Analog GND                                                                                                                   |  |  |  |  |

| 2    | AVDD      | Р   | -                     | Analog VDD 2.8V It should be tied with nearby AGND by 1uF bypass capacitors.                                                 |  |  |  |  |

| 3    | ATEST     | 0   | -                     | Analog test output                                                                                                           |  |  |  |  |

| 4    | AGND      | Р   | -                     | Analog GND                                                                                                                   |  |  |  |  |

| 5    | DGND      | Р   | -                     | Digital (Core) GND                                                                                                           |  |  |  |  |

| 6    | DVDD      | Р   | -                     | Digital (Core) VDD 1.2V DC It should be tied with nearby DGND by 1uF bypass capacitors.                                      |  |  |  |  |

| 7    | VREFN1    | 0   | -                     | VREFN1 output. It should be tied with nearby AGND by 1uF bypass capacitors.                                                  |  |  |  |  |

| 8    | VREFP1    | 0   | _                     | VREFP1 output. It should be tied with nearby AGND by 1uF bypass capacitors.                                                  |  |  |  |  |

| 9    | VREFP2    | 0   | -                     | VREFP2 output. It should be tied with nearby AGND by 1uF bypass capacitors.                                                  |  |  |  |  |

| 10   | VREFP3    | 0   | -                     | VREFP3 output. It should be tied with nearby AGND by 1uF bypass capacitors.                                                  |  |  |  |  |

| 11   | VREFP4    | 0   | -                     | VREFP4 output. It should be tied with nearby AGND by 1uF bypass capacitors.                                                  |  |  |  |  |

| 12   | AVDD      | Р   | -                     | Analog VDD 2.8V It should be tied with nearby AGND by 1uF bypass capacitors.                                                 |  |  |  |  |

| 13   | OGND      | Р   | -                     | Analog GND for OTP                                                                                                           |  |  |  |  |

| 14   | STDBY     | I   | pulldown              | Power stdby mode. When Stdby ='1', there's no current flow in any analog circuit branch, neither a ny beat of digital clock. |  |  |  |  |

| 15   | DVDD      | Р   | -                     | Digital (Core) VDD 1.2V DC It should be tied with nearby DGND by 1uF bypass capacitors.                                      |  |  |  |  |

| 16   | DGND      | Р   | -                     | Digital (Core) GND                                                                                                           |  |  |  |  |

| 17   | HVDD      | Р   |                       | IO VDD 1.8V ~ 2.8V DC It should be tied with nearby DGND by 1uF bypass capacitors.                                           |  |  |  |  |

| 18   | SDA       | BIO | pullup                | 2-wire serial interface clock, SDA line is pulled up to HVDD by off-chip resistor                                            |  |  |  |  |

| 19   | SCL       | BIO | pullup                | 2-wire serial interface data, SCL line is pulled up to HVDD by off-chip resistor                                             |  |  |  |  |

| 20   | X1        | I   | pulldown              | Master clock input pad                                                                                                       |  |  |  |  |

| 21   | DVDD      | Р   | -                     | Digital (Core) VDD 1.2V DC It should be tied with nearby DGND by 1uF bypass capacitors.                                      |  |  |  |  |

| 22   | DGND      | Р   | -                     | Digital (Core) GND                                                                                                           |  |  |  |  |

| Ball Name   IO   Pull up/ Pull down   PAD clock Data can be latched by external devices at the rising or falling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ntal window of interest. It ca |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| HSYNC O pulldown Horizontal synchronization pulse. HSYNC is high (or low) for the horizon n be programmed to appear or not outside the vertical window of interest VSYNC O pulldown Vertical sync: Indicates the start of a new frame  26 D11 O pulldown Digital Output bit 11  27 D10 O pulldown Digital Output bit 10  28 DGND P - Digital (Core) GND  29 DVDD P - Digital (Core) VDD 1.2V DC It should be tied with nearby DGND by 1uF bypass capacitors.  30 D9 O pulldown Digital Output bit 9  31 D8 O pulldown Digital Output bit 8  32 D7 O pulldown Digital Output bit 7  33 D6 O pulldown Digital Output bit 6  34 CKN/D5 O pulldown MIPI Clock Negative Output / Digital Output bit 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ntal window of interest. It ca |

| Pulldown n be programmed to appear or not outside the vertical window of interest vertical vertical window of interest vertical v |                                |

| Digital Output bit 11 Digital Output bit 11 Digital Output bit 10 Digital Output bit 10 Digital (Core) GND DVDD P DVDD P Digital (Core) VDD 1.2V DC It should be tied with nearby DGND by 1uF bypass capacitors.  Digital Output bit 9 DVDD Digital Output bit 9 Digital Output bit 8 DR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                |

| Digital Output bit 10 Digital Output bit 10 Digital (Core) GND Digital (Core) GND Digital (Core) VDD 1.2V DC It should be tied with nearby DGND by 1uF bypass capacitors.  Digital (Core) VDD 1.2V DC Digital (Cor |                                |

| Digital (Core) GND  Digital (Core) GND  Digital (Core) VDD 1.2V DC It should be tied with nearby DGND by 1uF bypass capacitors.  Digital Output bit 9  Digital Output bit 8  Digital Output bit 7  Digital Output bit 7  Digital Output bit 6  CKN/D5  Digital Output bit 6  MIPI Clock Negative Output / Digital Output bit 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                |

| DVDD P - Digital (Core) VDD 1.2V DC It should be tied with nearby DGND by 1uF bypass capacitors.  Digital (Core) VDD 1.2V DC It should be tied with nearby DGND by 1uF bypass capacitors.  Digital Output bit 9  Digital Output bit 8  Dr O pulldown Digital Output bit 7  Digital Output bit 7  Digital Output bit 6  CKN/D5 O pulldown MIPI Clock Negative Output / Digital Output bit 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                |

| lt should be tied with nearby DGND by 1uF bypass capacitors.  Description of the pulldown of t |                                |

| 31 D8 O pulldown Digital Output bit 8 32 D7 O pulldown Digital Output bit 7 33 D6 O pulldown Digital Output bit 6 34 CKN/D5 O pulldown MIPI Clock Negative Output / Digital Output bit 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                |

| 32 D7 O pulldown Digital Output bit 7  33 D6 O pulldown Digital Output bit 6  34 CKN/D5 O pulldown MIPI Clock Negative Output / Digital Output bit 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                |

| 33 D6 O pulldown Digital Output bit 6 34 CKN/D5 O pulldown MIPI Clock Negative Output / Digital Output bit 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                |

| 34 CKN/D5 O pulldown MIPI Clock Negative Output / Digital Output bit 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                |

| O Sulldown MID Cloth Paristic Control & District Control & Control |                                |

| 35 CKP/D4 O pulldown MIPI Clock Positive Output / Digital Output bit 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                |

| 36 DN1/D3 O pulldown MIPI DN1 Output / Digital Output bit 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                |

| 37 DP1/D2 O pulldown MIPI DP1 Output / Digital Output bit 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                |

| 38 DNO/D1 O pulldown MIPI DNO Output / Digital Output bit 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                |